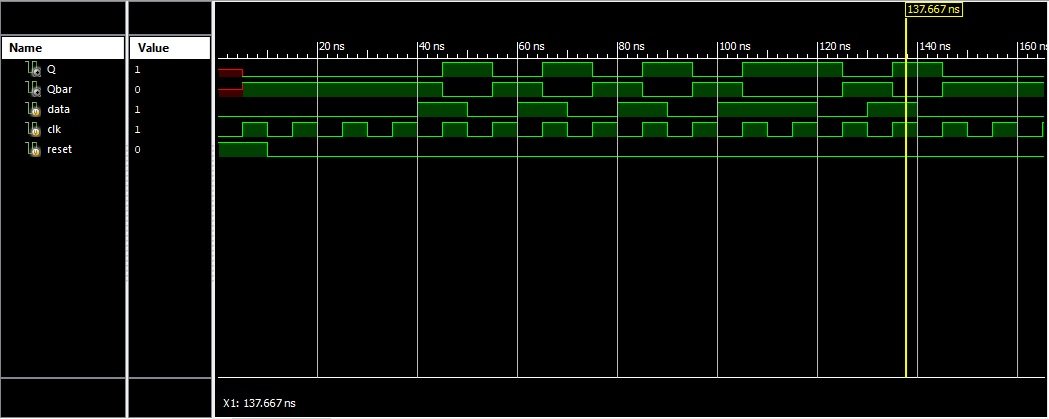

In designing sequential circuits we will see that using D flip flop is the easiest to way to design any sequential circuit. Q 0) and the triangle after the bubble determines edge triggering. Thus a change in the output of the flip flop can be triggered only by and during the transition of the clock from 1 to 0.Īlways clk) // whenever clk goes from 1 to 0,then change the output

The Master latch is disabled because clock=0. The slave latch is enabled, and its output Q is equal to the master output Y. An edge-triggered flip-flop changes state either at the positive edge (rising edge) or at the negative edge (falling edge) of the clock pulse. When the clock is 0, the output of the inverter is 1. Flip-flops are synchronous: the output changes state only at a specified point on the triggering input called the clock (CLK) In other words, changes in the output occur in synchronization with the clock. The circuit samples the D input and changes its output only at the negative edge of the synchronizing or controlling clock. The first latch is called the master and the second the slave.

The construction of a D Flip Flop with 2 D latches and an inverter is made in order to give it an edge triggered sequential device.

0 Comments

Leave a Reply.AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed